# 表面再構成制御成長法による Si 上 InSb 量子井戸作製と その超高速 FET への応用

研究代表者 理工学研究部(工学) 前澤 宏一 非常勤研究員 斉藤 光史

#### 研究成果

InSb は高い電子移動度、電子飽和速度を持つことから、高速低消費電力デバイスへの応用可能性を示唆されてきた。しかし、InSb は大きな格子定数を持つため、基板となる材料との格子不整合という大きな問題を抱えていた。近年、インテルによって GaAs 基板上での InSb 量子井戸トランジスタ(QW-FET)が発表された事によって、本質的に高性能な InSb を実際のデバイスへ応用しようとする試みが活発になっている。

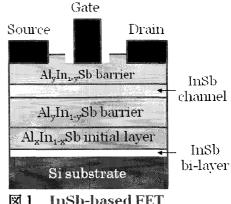

我々の研究においては基板材料として Si を用いている。現在最も研究が進んでいる Si デバイスとの組み合わせという観点からも、また、低コスト化の点からも、Si 上での InSb-based デバイスの研究はとても有意義なものであるが、Si/InSb 間の 19.3%もの大きな格子不整合がその実現の妨げとなっている。我々の研究により、Si(111)上へ InSb 単分子層(InSb bi-layer)を介して InSb 層を成長させることによって、Si 上で面内方向に 30° 回転した InSb 層を得ることができ、このときの InSb/Si 間の格子不整合が見かけ上、約 3.3%にまで減少することが明らかになった。本プロジェクトではこの現象を応用し、図1に示すような構造を持った InSb トランジスタの試作を最終目標としている。

トランジスタ構造を得るために、品質の良いバリア層の形成が必要となる。当面の課題はバリア層としての AlSb、もしくは AlInSb 層を Si 基板上に形成することであり、前述の InSb 層の面内回転効果を、これらのバリア層形成に応用できるか検証することである。 AlSb において、InSb と同様な 30°回転を実現することができれば、Si 基板との格子不整合は、非回転時に 14.8%であるものが 約-2.2% にまで減少することが期待される。 $Al_xIn_{(l-x)}Sb$  と Si の格子不整合は、30°回転時に  $3.3\sim-2.2\%$  ( $x=0\sim1$ )となる。以下に本年度の主な研究内容、及び得られた知見を簡単に示す。

図 1 InSb-based FET on Si substrate

# i) InSb bi-layer 中の In 層及び Sb 層の役割についての検討

品質のよい 30°回転した InSb 薄膜を得るためには In 層及び Sb 層の両方が必要となる、つまり、InSb bi-layer を介する事が必要となるということを明らかとした。

### ii) Si 基板上での AlSb 単分子層の形成の試み

Si 基板上での Al 原子と Sb 原子の相互作用は In 原子と Sb 原子の相互作用と似たものであったが、これを Si 基板上での AlSb 薄膜形成に応用するとき、InSb 薄膜の場合のような 30° 回転が起こらないことが明らかとなった。

#### iii) InSb bi-laver/Si 基板上への高品質 AISb 薄膜形成の試み

どの様な条件下においても非回転の結晶と回転した結晶が混在したもの、あるいは非回転

の結晶のみのものとなり、良好な結果を得ることができなかった。

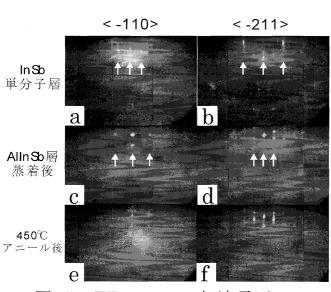

### iv) InSb bi-layer/Si 上への、Al<sub>x</sub>In<sub>(1-x)</sub>Sb 薄膜形成

AlSb よりも低い温度で作製することができる  $Al_xIn_{(1-x)}Sb$  ( $x=0.1\sim0.3$ )薄膜の InSb bi-layer/Si 基板上での形成を試みた。Ts= 240℃において膜厚 30nm の Al<sub>x</sub>In<sub>(1-x)</sub>Sb (x=0.1)を作製した結果、 この AlInSb 層が Si 基板に対して 30°回転していることが分かった。図2に示される高速電 子線回折(RHEED)像において、AllnSb の蒸着前(a, b)と、蒸着後(c, d)では<-110>方向から観察 したストリーク(矢印で示す)間隔と<-211>方向から観察したストリーク間隔とが入れ替わっ ていることが見て取れる。これは前述した InSb 薄膜の 30°回転の場合と同じであり、AlInSb 層の 30°回転を示唆している。 同様な条件で作製した AlInSb 薄膜の(111)面に対する XRD φ -scan を図3に示す。基板の Si(111)面に対する $\phi$ -scan からのピークに対して30° ずれて6本 のピークが観察されることからも、AlInSb層が30°回転していることは明らかである。図2 (e, f)に AlInSb 層蒸着後、Ts= 450℃でアニールした後の RHEED イメージを示す。蒸着後(c, d) にはアイランドパターンを示していたものが、アニール後ではストリーク状に変化し、更に 1/2 ストリークが現れている。これより、この温度において表面性が改善されていることが分 かる。更に基板温度を上げても、Ts= 520℃まで AlInSb の RHEED パターンが観察された。こ のことから、ここで形成された AlInSb 層が Ts= 520℃まで利用できることが示唆される。  $Al_xIn_{(1-x)}Sb$  (x=0.1)層上へ、更に Al 組成の大きな  $Al_xIn_{(1-x)}Sb$  層の蒸着を考えたとき、必要とな る基板温度は最高で 520℃程度(y =1: AlSb)である。それゆえ、ここで作製した Al<sub>x</sub>In<sub>(l-x)</sub>Sb (x=0.1)層上で適度な Al 組成比を持った  $Al_v In_{(1-v)}Sb$  層 $(y=0.2\sim0.4)$ の形成が期待される。

## 研究成果から期待される今後の展望

前述図1で示した、最終目標として考えるトランジスタ構造を形成するにあたり、最大の 問題点は、Al<sub>x</sub>In<sub>(1-x)</sub>Sb initial layer / Si 積層界面に存在する大きな格子不整合である。今年度の 研究によって、この問題に対する一定の成果を得る事ができた。これにより、今後、各層作 製条件の最適化、及び、AlInSb 系のデバイス作製プロセスを検討することで、実際のトラン ジスタ構造を試作することができると期待される。